## AN ADVANCED CROSSBAR SWITCH FOR INTEGRATED DESIGN

# ANKIT SINGH<sup>a1</sup> AND HEMLATA SINHA<sup>b</sup>

<sup>ab</sup>SSIPMT Raipur, Chhattisgarh, India

## ABSTRACT

The paper represents a technique or methodology to develop a crossbar switch which is of reconfigurable architecture for network processors. The main objective of this paper is to enhance the performance of crossbar and reduce the excess power consumption. The method we proposed to reduce the power consumption at the runtime of crossbar switch is to enable only those link connection of crossbar which are necessary for the circuit or switch to perform and the unnecessary connection link turn off or disable by sending signal. We implemented a parameterized register transfer level design of reconfigurable crossbar switch. In this paper we have shown the result of 4×4 crossbar switch including the VHDL simulation of Reconfigurable Crossbar Switch on Xilinx ISE software tool.

KEYWORDS: Interconnection Network; On-chip Communicatio;, Reconfiguratio Crossbar Switch;

Before the end of nineties, network equipment generally used as a general-purpose processors. But the need of quality-of-service (QoS) and the high speed data transmission asked for a quick evaluation of network equipments. Thus, the Network processor (NP) [1], [2] was created. Network processor takes the place of general-purpose Processors and Application specific Integrated circuits in network equipments. This are used to improve the two important issues flexibility and performance. These two features of processors are essential to process the packets, and the network processor is a best option to get them.

As industries build multi-core architecture involving number of cores in the future, on-chip interconnection network becomes a number one candidate for solving the problem facing on current multiprocessor chip. However one of the major challenges currently faced by on-chip interconnection is the power consumption [3]. NoC architecture classified by the links for packet data transmission and router for storing, arbitration and switching functions performed by input buffer, arbiters and the crossbar respectively power is consumed from both communicating data packets across links as well as from switching and storage within the router [12]. With the increased need of low power architectures, research has focused on optimizing buffer design [9],[10],[11] minimizing crass-power [8] and utilizing 3D interconnection [13]. The effective sharing of channel is achieved by implementing routing, crossbar switch within the router on a hop-by-hop basis. The motivation is to increase the above two features cited before. With the help of reconfigurable crossbar switch in a network processor it could be achieved. Hence, using network processor with a reconfigurable crossbar switch as interconnection structure, it is possible to increase the throughput and reduce the power consumption of the network processor and also reduce the latency in communication packet transfer. The main objective of this paper is to reconfigure crossbar switch, a reconfigure crossbar switch architecture used to connect different inputs and outputs in interconnection and communication networks, and to implement dynamically topologies in two reconfiguration level. the reconfigurable crossbar switch was described in VHSIC Hardware Description Language and implemented in the Field Programmable Gate Array. The outputs show the behavior of the application which contains transfer of packets that perform a collective broadcast operation on the reconfigurable crossbar switch.

#### ORGANIZATION

There are number of commercial network processor of many companies available at the market. Some of this companies and their respective network processor are [1]: IBM (NP4GS3), Motorola/C-port (C-5 Lucent/Agere (FPP/RSP/ASI), family), Sitera/Vitesses (IQ2000), Chamelean (CS2000), EZChip (NP-1), Intel (IXPI1200) and many more. None of them gives reconfigurability except the CS2000 of Chamelean [6]. But it does not have reconfigure crossbar switch. Network processor architecture has blocks to execute some function as a Network Processor System-on -Chip. Some of those blocks are PCI units, memory units, packet classifications, policy engines, metering engines, packet transform engines, queue engine, QoS engines and some other blocks. There are some papers about crossbar switch but they use reconfiguration crossbar in a network processor. the related works [2],[5] presents result of previously implemented crossbar switch on FPGA. Our proposed platform for implementing crossbar switch with reduced energy consumption, flexibility but it did not change the core architecture. The work proposed is based on signal handling but the reconfiguration is depended on the FPGA. The Flexbar [7] work propos to modify schedules and network hardware level, but the crossbar

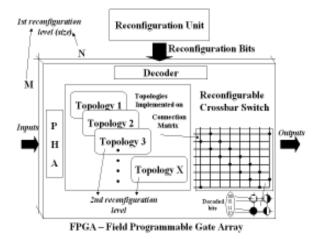

architecture is similar to a traditional crossbar switch (TCS). This paper done not relate the FPGA and reconfigure switch as a feature of flex bar Fig 1: FPGA – Reconfigurable Crossbar Switch

Figure 1: FPGA – Reconfigurable Crossbar Switch

The fig. 1 shows architecture of FPGA-Reconfigurable Crossbar Switch. Fig.1 shows some connection nodes of the reconfigurable crossbar switch, which if closed compose a circuit. This circuit represents a topology in space. Differ from the traditional crossbar switch where it is possible to close only one node per line or per column regarding the implemented topology, the Reconfigurable Crossbar Switch permits that more than one node can be closed per line or column at the same time . The reconfigurable crossbar switch uses a reconfiguration bits to implement the topology in the space. This topology is used to create the connection as for the circuit. The reconfigurable bits set are capable of reconfigurable crossbar switch whenever it required.

The architecture of a bidirectional channel network-on-chip (BiNoc) router model [14]. This part of network is used to enhance the performance of on-chip communication. In BiNoc, every communication channel allows itself to be dynamically reconfigured to transmit fits in one direction. This added flexibility, better bandwidth utilization, lower packet delivery latency and higher packet consumption rate. NoC router architecture is developed to support self configuration of the bidirectional traffic flow in the network processor. The flow direction at every channel-direction-control protocols (CDC) [14]. This channel-direction-control protocol provides high performance, free of deadlock and free of starvation. Following points also illustrate reconfigurable crossbar switch components of a BiNoc router.

#### **Crossbar Traversal**

Flits that grant passage on the crossbar passed to the appropriate output channel.

## **Switch Allocation**

Individual flits arbitrate for access to all physical characters via the crossbar on each cycle. Arbitration may be performed in two different stages [5]. The first stage reflects the sharing of a single crossbar port by V-input arbitrate between winning request from each input for each output channel. The request for a particular output port is routed from the VC which wins the second stage of arbitration. In order to improve fairness, the stage of the V-input the second stage of arbitration. We have to assume this organization wherever multiple stage of arbitration is presents.

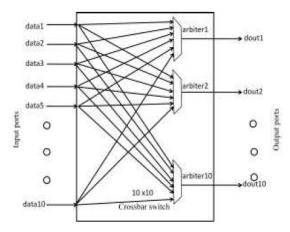

### Arbiter

Arbiter controls the arbitration of the ports and resolves connection problem. It keeps the update status of all the ports are free and which ports are communicating with each other. Fig.3 shows the arbiters used in the Reconfigurable Crossbar Switch.

Figure 2: Arbiters in Crossbar Switch Model

Packets with the same priority and destined for the same output port are scheduled with round-robin arbiter.

#### Crossbar

A crossbar switch is a switch connecting multiple inputs to multiple outputs in a matrix manner. The design of crossbar switch has 4 inputs and 4 outputs. In architecture illustration in fig.2 each input port is forced to share a single crossbar port even when multiple flits could be sent from different virtual-channel buffer. This restriction allows keeping crossbar size small and independent of the number of virtual-channel.

#### **Reconfigurable Crossbar Switch Architecture**

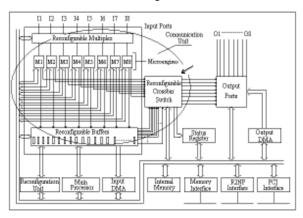

The figure 3 shows the Reconfigurable RISC Network processor (R2NP) architecture [4]. R2NP is generally used as a base for developing or design of our reconfigurable crossbar switch architecture. Thus, design of our reconfigurable crossbar switch was based on the R2NP in network processor.

Reconfigurable crossbar switch shown in figure 1, has mainly three blocks: (1) connection matrix, where all the topologies are implemented; (2) decoder, that converts the reconfigurable bits for a matrix bits set and (3) pre-header analyzer. Network processor can add this third block in the packet with the output destination. Reconfigurable crossbar switch (RCS) uses reconfiguration bits to implement the topology in the space. Only the Reconfiguration Unit and instruction set of the network processor are able to change those bits in order to implements new topologies. Although one instruction can modify the 01 and 10 formats the 00 format is restricted to reconfiguration unit.

Figure 3: FPGA – R2NP Architecture

In this paper we proposed a method to develop reconfigurable crossbar switch architecture for network processor. In this paper we used  $4 \times 4$  crossbar switch.

#### **Proposed Work**

In this paper we proposed a method to develop reconfigurable crossbar switch architecture for network processor. In this paper we used  $4 \times 4$  crossbar switch. in  $4 \times 4$  crossbar switch for 4 inputs and 4 outputs 16 connections are formed. If the 12 connections enable and other connections are disable although the power is consumed by all the connection in the switch. This power consumption is very big when the crossbar switch is used in very large scale. This becomes a disadvantage for crossbar switch. So in our proposed method we check whether the packet data comes from input is normal data or configured data. If the input packet is normal data then we allow it pass, but if the input packet is configured data then we stop the next packet and convert it into crossbar matrix.

Fig.4 shows the crossbar matrix. By use crossbar matrix we are able to start and stop a connection enable the signal. By stopping the unused connection

#### **Figure 4: Crossbar Matrix**

#### **Experimental Result**

In our first result we have demonstrated the output of a normal packet from sources, 00,01,10 and 11 to 01,10,11,00 respectively. Our results show that the data goes properly from the given source towards the destination. The normal packets have MSBs as 0000

**Figure 5: FPGA Result**

In our next result, we demonstrate the reconfiguration, here we can observe that the connection matrix changes thereby the links which are turned off cannot communicate between each other.

## REFERENCES

- D. E. Comer, "Network Systems Design using Network Processors", Prentice Hall, 2003

- G. Lawton, "Will Network Processor Units Live up to Their Promise?", IEEE Computer, Volume 37, Number 4, April, 2004, pp.13-15

- H. S. Wang, L. S. Peh, and S. Malik, "Power-driven design of router micro architectures in on-chip networks," in Proceedings of the 36th Annual ACM/IEEE International Symposium on Micro architecture, Washington DC, USA, December03-05 2003, pp. 105–116.

- H. C. Freitas and C. A. P. S. Martins, "Didactic Architectures and Simulator for Network Processor Learning", Workshop on Computer Architecture Education, San Diego, CA, USA, 2003, pp.86-95.

- K. Mai," Smart Memories: A Modular Reconfigurable Architecture," Proc ISCA, June 2000, pp. 161-71.

- S. E. Dongkook Park, R. Das, A. K. Mishra, Y. Xie, N. Vijaykrishnan, and C. R. Das, "Mira: A multilayeredon-chip interconnect for router architecture," in Proceedings of the International Symposium on Computer Architecture (ISCA), June 2008, pp. 251–261.

- Ying-Cherng Lan, Hsiao-An Lin, Shih-Hsin Lo, Yu Hen Hu, and Sao- Jie Chen, "A bidirectional noc (binoc) architecture with dynamic self reconfigurable channel," Computer-Aided Design of Integrated.

- J. D. Owens, W. J. Dally, R. Ho, D. N. Jayasimha, S.W. Keckler, and L. S. Peh, "Research challenges foron-chip interconnection networks," IEEE Micro, vol.27, no. 5, pp. 96–108, September-October 2007.

- H. S. Wang, L. S. Peh, and S. Malik, "Power-driven design of router micro architectures in on-chip networks," in Proceedings of the 36<sup>th</sup> Annual ACM/IEEE International Symposium on Micro architecture, Washington DC, USA, December03-05 2003, pp. 105–116.

- J. Hu and R. Marculescu, "Application-specific buffer space allocation for network-on-chip router design," in Proceedings of the IEEE/ACM International Conference on Computer Aided Design (ICCAD), SanJose, CA, USA, November 7-11 2004, pp. 354–361.

- C. A. Nicopoulos, D. Park, J. Kim, N. Vijaykrishnan, M. S. Yousif, and C. R. Das, "Vichar: A dynamic virtual channel regulator for network-on-chip routers," in Proceedings of the 39th Annual International Symposium on Micro architecture (MICRO), Orlando, FL, USA, December 9-13 2006, pp. 333–344.

- W. Dally, "The J-Machine Network" Proc Intnl Conf on Computer Design. IEEE VLSI in Computer & Processor, Oct 1992, pp 420-423.

- S. E. Dongkook Park, R. Das, A. K. Mishra, Y. Xie, N. Vijaykrishnan, and C. R. Das, "Mira: A multilayeredon-chip interconnect for router architecture," in Proceedings of the International Symposium on Computer Architecture (ISCA), June 2008, pp. 251–261.

Ying-Cherng Lan, Hsiao-An Lin, Shih-Hsin Lo, Yu Hen Hu, and Sao- Jie Chen, "A bidirectional noc (binoc) architecture with dynamic self reconfigurable channel," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, vol. 30, no. 3, pp. 427 – 440, march.